| UART串口调试项目 | 您所在的位置:网站首页 › 串口 调试 › UART串口调试项目 |

UART串口调试项目

|

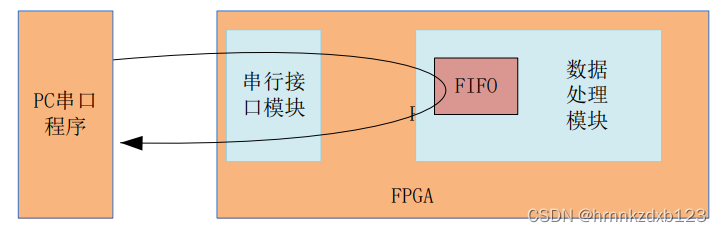

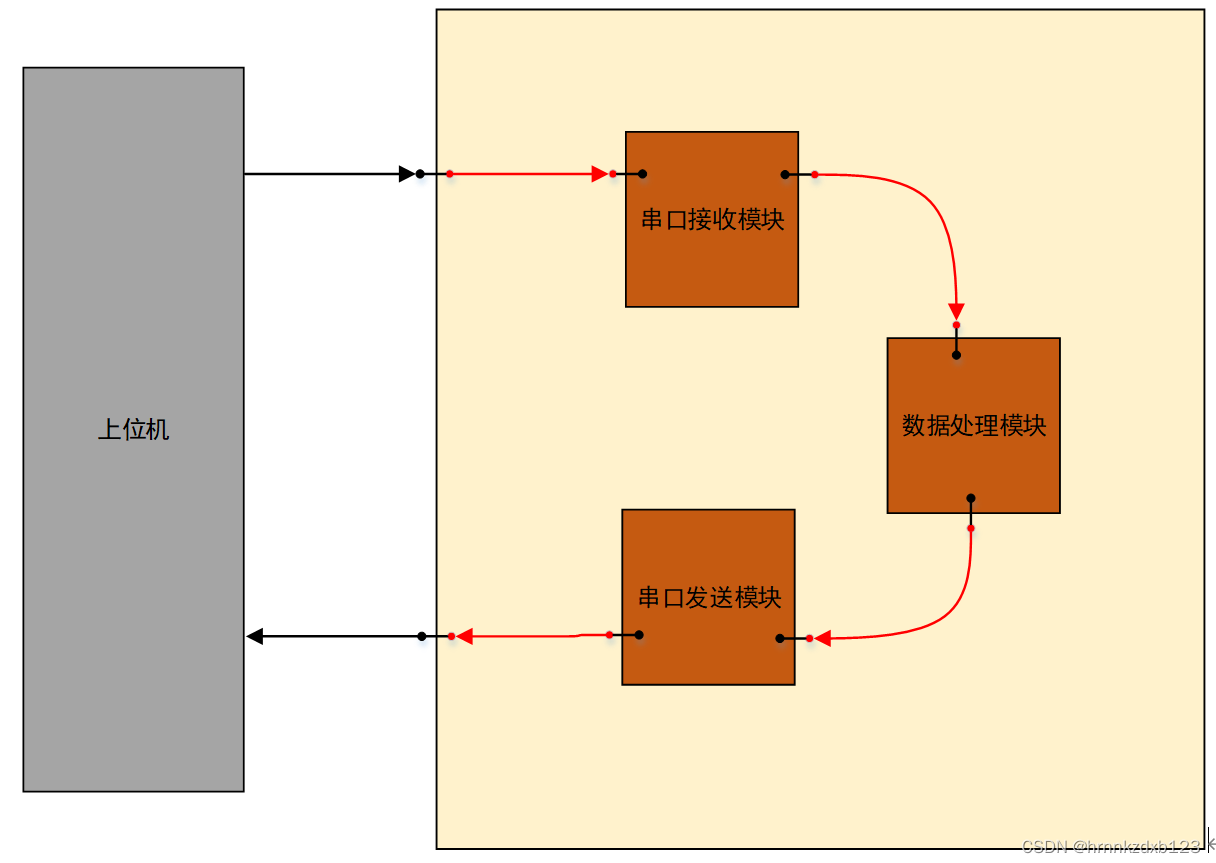

一、简介

本文实现的是串口回环功能

其具体功能如下:

其具体功能如下:

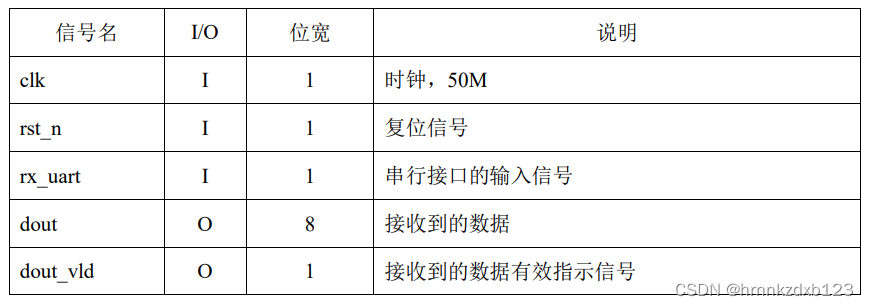

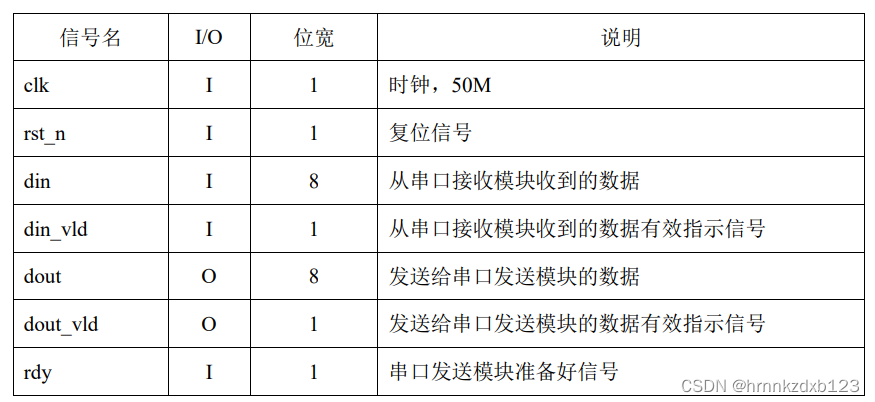

(1)FPGA内部有一个可保存128字节的FIFO; (2)FPGA从上位机接受到数据后,将数据保存到FIFO中; (3)当FPGA保存的数据超过60个数据时,启动发送数据操作:读取FIFO的数据,将数据返还给上位机; (4)在启动发送数据操作过程中,如果FIFO变空,结束发送操作,等待下一次的启动; (5)上位机接受到的数据必须与发送的数据相同,不能多不能少。 该串行接口的参数如下:波特率:9600; 无校验位; 数据位:8位; 停止位:1位; 按十六进制发送接收。 二、接收模块信号列表:

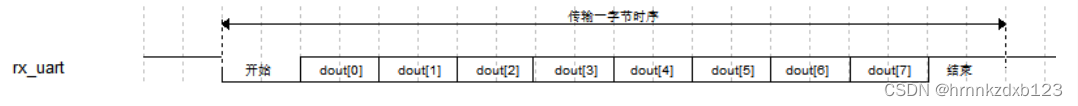

rx_uart与PC连接的串口线,其时序如下图:

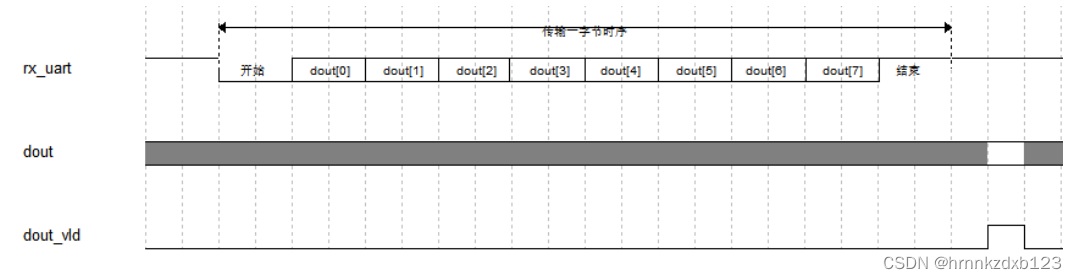

注意:波特率是9600,时钟是50M,时钟周期是1s/50MHz=20ns,波特率是9600,需要1s/9600≈104167,大约需要104167/20≈5208个时钟周期。 dout和dout_vld是从串口接收到的数据和提示信号。上面的时序每出现一次,本模块就开始接收,接收到的数据保存到dout当中。当完全接收到一个字节后,dout_vld产生一个高电平来表示。其时序图如下所示:

要注意:dout_vld高电平仅是一个时钟周期(20ns)。下游模块检测到这个信号,每次看到其为1,就表示收到了一个字节的数据。 三、处理模块信号列表

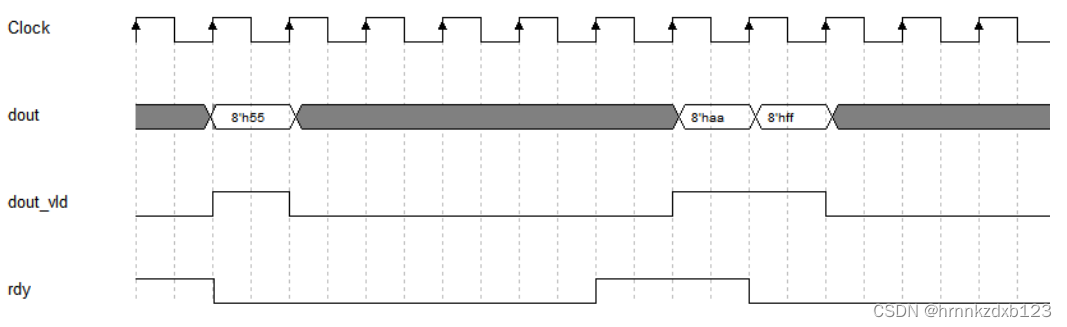

din和din_vld就是从串口模块接收到的字节数据,本模块要将其保存到FIFO当中。 当内部FIFO的个数保存超过60个时,开始将其输出到串口发送模块。但是需要注意,只有rdy==1时,即发送模块准备好时,才能发送。其正确的时序如下:

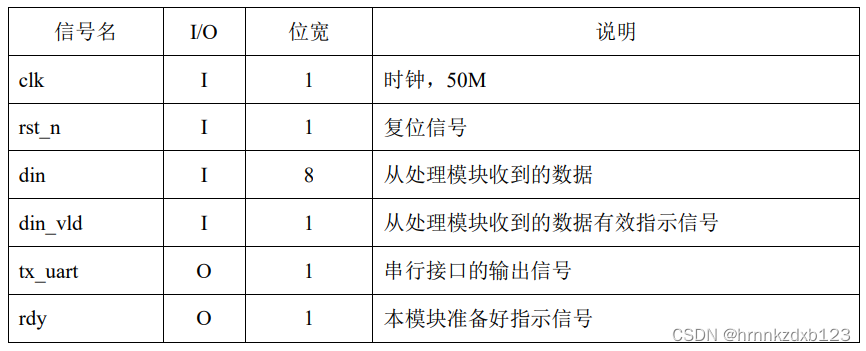

在时钟沿前,看到rdy==1时,上升沿后dout_vld==1,表示发送。本模块只要遵守此规则就可以了。如果不遵守此规则,肯定是本模块的问题,如果遵守了此规则,但仍然有错,都不是本模块的问题。 另外,本模块用到了FIFO,FIFO也可能会出错的,但都是使用FIFO的错误。 四、发送模块信号列表

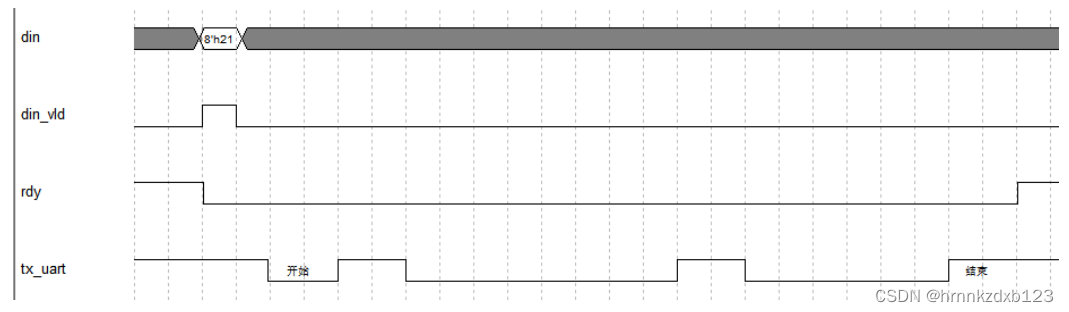

本模块的时序如下图所示:

模块收到din_vld有效时,就将对应的的值(8'h12),按照串口时序发送给PC。在忙碌期间,rdy==0,要求上游模块不要发送数据过来。尤其时需要注意以下几点: 1.rdy 见到 din_vld 等于 1 时,必须立刻变低,不要等下一拍。只要这样,才能实现:一个字节 一个字节发送数据的目的。 2. 在处理数据期间,rdy 要一直为 0。 3. 要发送的数据,仅仅是 din_vld=1 所对应的数据,其他时候数据都不关心。 |

【本文地址】